- #State transition diagram altera quartus ii manual

- #State transition diagram altera quartus ii software

- #State transition diagram altera quartus ii code

- #State transition diagram altera quartus ii download

Wait until rising_edge(clk) and g(3) = '1' Īnd this is as close as I could get with ghdl and gtkwave: Wait until rising_edge(clk) and g(2) = '1' Wait until rising_edge(clk) and g(1) = '1' Signal r: std_logic_vector(1 to 3) := (others => '0') You can use it to insure the arbiter works as intended even if you can’t display state: library ieee I wrote a test bench that reproduces the waveform from the book. I’d suggest you you delete state from the simulation display and re-add it insuring it matches Figure 29 on of the tutorial you provided the link for, above. We also created 4 × 4 and 7 × 7 Moore neighborhood versions. One version uses a 4 × 4 von Neumann neighborhood as depicted in Fig. I’ve followed them exactly but that SIGNAL is still showing up as undefined no matter what. Using Altera Quartus-II’s GUI interface, 3 versions of the CA machine were created and simulated. The directions for this are on pages 27 to 29. I’ve even followed the directions provided by Altera in the below linked pdf. The Machine State is the Y variable, which is showing an ENUM like Quartus is supposed to. The book, in a different example shows the FSM’s state just fine. Here is a screenshot of the Finite State Machine Implemented in Quartus: The Machine State Variable which is a VHDL SIGNAL in the FSM’s Architecture won’t show as anything other than Undefined, even though the FSM is working fine. Make sure that the FSM properly transitions between states as displayed on the red LEDs, and that it produces the correct output values.Before beginning a larger project in Quartus II I’m trying to do the section 8.8 “FSM as an Arbiture Circuit” example from the book “Fundamentals of Digital Logic with VHDL Design 3rd ed” and I can’t get Quartus to work like it’s supposedly documented. Test the functionality of your design by applying the input sequences and observing the output LEDs.

#State transition diagram altera quartus ii download

Once you are confident that the circuit works properly as a result of your simulation, download the circuit into the FPGA chip.

#State transition diagram altera quartus ii code

any experts in quartus II can help me solve this, if cant astate diagram or a way to code is also very helpful.

#State transition diagram altera quartus ii manual

Include the Verilog file in your project, and assign the pins on the FPGA to connect to the switches and the LEDs, as indicated in the User Manual for the DEI board. Experts Quartus Ii Help Solve Cant State Diagram Way Code Also Helpful Thanks Advance Use Q43486560. Use the green light LEDGO as the output of green light signal, LEDRO,LEDRI and LEDR2 as the output of red light signal. DOI: 10.

Write a Verilog code or use FSM diagram tool that represent the circuit and use the toggle switch SWO on the DEl board as an active-low synchronous reset input for the FSM, use SW1, SW2, SW3, SW4 as the camera input. is specified either by means of a schematic diagram, or by using a.

#State transition diagram altera quartus ii software

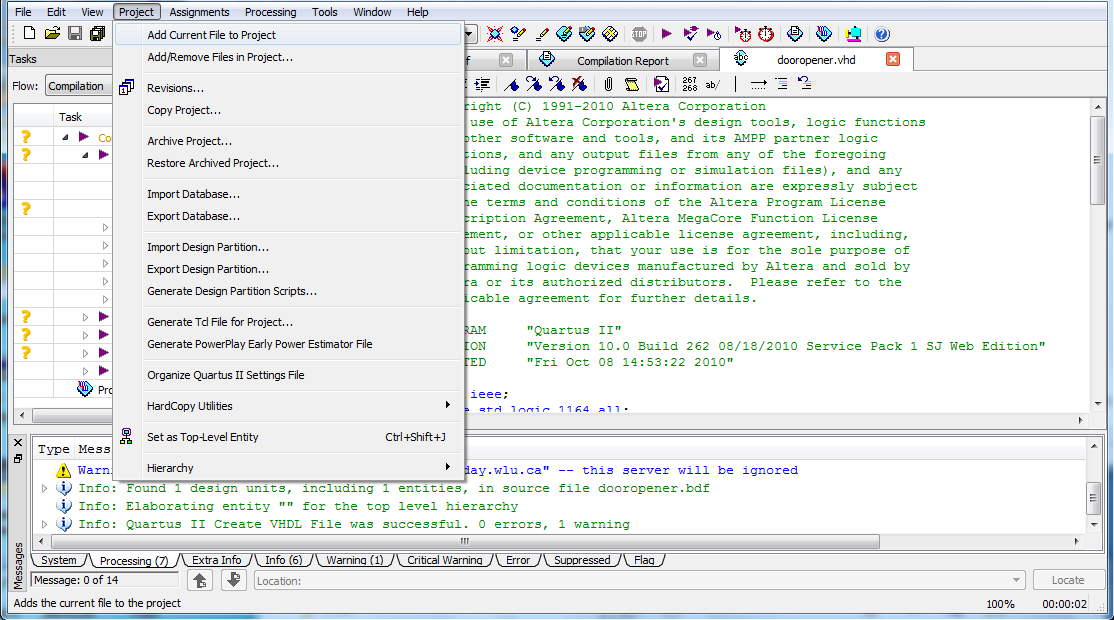

Select as the target chip the Cyclone II EP2C20F484C7, which is the FPGA chip on the Altera DEI board. the Quartus II software to implement a very simple circuit in an Altera FPGA device. Create a new Quartus II project for the FSM circuit. Lab Assignments Select one of your Design alternatives and implement it on the DE1 board as follows: 1. branch -1000 Ooo branch D In other word: system has at least these inputs (counter, camera B, camera C, camera D), also it has at least these four outputs (one traffic light signal is green and all other is red). In case current active camera shows there no car in active branch traffic light controller should make current light signal red and move to next branch. The regular cycle for each signal is 30 second green each as long if there are cars in that light. At each light signal there is connected camera, so there is three cameras B,C,D. branch B Background Consider the problem of controlling a traffic light at the intersection of T streets, so there is three branch, B,C,D. Altera DE1 Board user manual and Exercises.

0 kommentar(er)

0 kommentar(er)